VHDL的Testbench编程指导

介绍:

VHDL(Very HighSpeed Integrated Circuit Hardware Description Language)是一种硬件描述语言,用于描述数字系统的结构和行为。在VHDL中,Testbench是用于模拟和验证设计的一种描述。

本文将为您提供有关VHDL Testbench编程的一些建议和指导,帮助您创建有效的测试环境和测试代码。

1. 理解Testbench的作用和结构:

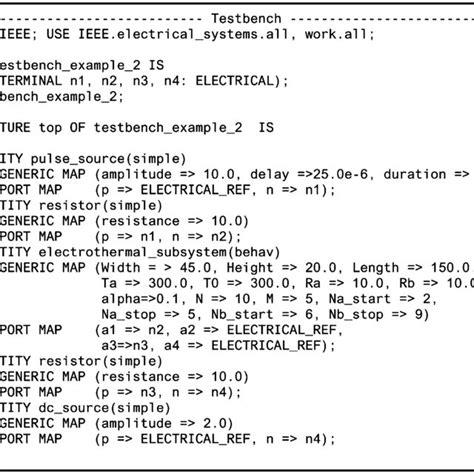

Testbench是一个独立于设计的实体,用于模拟和验证设计的功能。它通过创建输入信号并捕获和分析输出信号来确认设计的正确性。

Testbench的结构通常包括以下部分:

实例化设计:将待测试的模块实例化,并为其提供适当的输入信号。

生成时钟:生成一个时钟信号用于驱动设计的时钟输入。

提供输入信号:为待测试模块的输入信号提供适当的值和时序。

捕获和分析输出信号:检查待测试模块的输出信号,比较其与预期结果是否一致。

2. 编写模块的实例化:

在Testbench中,首先需要实例化待测试的模块。这样您就可以访问模块的输入和输出端口,并为其提供适当的信号值。例如:

```

DUT: entity work.my_module

port map (

input_1 => input_signal_1,

input_2 => input_signal_2,

output => output_signal

);

```

其中,`my_module`是您要测试的模块的名称,`input_signal_1`和`input_signal_2`是您为输入信号定义的信号,`output_signal`是您为输出信号定义的信号。

3. 生成时钟信号:

大多数设计都需要时钟信号来驱动其操作。在Testbench中,您需要生成一个适当的时钟信号,并为模块的时钟输入提供该时钟信号。例如:

```

process

begin

clk_signal <= '0';

wait for 5 ns;

clk_signal <= '1';

wait for 5 ns;

end process;

```

这段代码将生成一个周期为10ns的时钟信号,并将其赋给`clk_signal`。

4. 提供输入信号:

在Testbench中,您需要为模块的输入信号提供适当的值和时序。您可以使用`process`或`testcase`语句来定义输入信号的行为。例如:

```

process

begin

input_signal_1 <= '0';

input_signal_2 <= '1';

wait for 10 ns;

input_signal_1 <= '1';

input_signal_2 <= '0';

wait;

end process;

```

上述代码将定义了一个简单的输入信号模式,其中`input_signal_1`和`input_signal_2`分别在10ns处发生变化。

5. 捕获和分析输出信号:

在Testbench中,您可以使用`assert`语句来检查模块的输出信号是否符合预期。例如:

```

process

begin

wait for 20 ns;

assert output_signal = '1' report "Output signal is not as expected";

wait;

end process;

```

上述代码将在20ns后检查`output_signal`是否等于1,并在不符合预期时输出错误信息。

6. 运行仿真:

在VHDL仿真工具中,您可以执行Testbench来验证设计的正确性。执行仿真时,Testbench将生成输入信号并捕获输出信号,您可以通过观察输出结果和报告来判断设计是否正常工作。

VHDL Testbench编程是验证和确认设计正确性的重要环节。理解Testbench的作用和结构,并使用适当的实例化、时钟生成、输入信号提

文章已关闭评论!

2024-11-26 14:39:34

2024-11-26 14:38:19

2024-11-26 14:37:11

2024-11-26 14:35:53

2024-11-26 14:34:35

2024-11-26 14:33:09

2024-11-26 14:31:56

2024-11-26 14:30:46